# Incapacitating the Competition: The Impact of Vertical Restraints on Technology Adoption

Laura Grigolon and Michelle Sovinsky\*

January 8, 2026

## Abstract

Vertical restraints imposed on some downstream buyers can affect non-contracted firms by weakening upstream suppliers' effective viability. We study these contracting externalities using Intel's exclusionary agreements with PC manufacturers in the microprocessor market. Combining litigation-based measures of restraints with PC data, we estimate dynamic models of AMD adoption that allow for cross-buyer spillovers. We find that exclusivity imposed on a given buyer significantly reduces adoption by other, non-contracted buyers, generating sizable and persistent market-wide effects. The paper provides the first empirical quantification of the economic magnitude of contracting externalities and highlights the broader competitive risks posed by exclusionary contracting.

JEL Codes: L42, L63, K21, D22

Keywords: contracting externalities, vertical restraints, semiconductors

---

\* Laura Grigolon: University of Mannheim and CEPR, [laura.grigolon@uni-mannheim.de](mailto:laura.grigolon@uni-mannheim.de); Michelle Sovinsky: University of Mannheim and CEPR, [Michelle.Sovinsky@uni-mannheim.de](mailto:Michelle.Sovinsky@uni-mannheim.de). Sovinsky acknowledges support from the European Research Council (ERC) Grant #725081 FORENSICS and from the German Research Foundation (DFG) through CRC TR 224 (Project B04). We are grateful for helpful comments from Luís Cabral, Chiara Fumagalli, Massimo Motta, Nicolas Schutz, Frank Verboven, and seminar participants at APIOS (Asia-Pacific Industrial Organization Conference), Barcelona Applied IO Workshop, Cambridge, CEPR Symposium, CREST Paris, Düsseldorf (DICE), EARIE, Edinburgh, EEA, European University Institute (EUI), European Competition Network Chief Economists Meeting, ETH Zurich, German IO meetings, Gothenburg, Hamburg, Hebrew University of Jerusalem, IIOC, Liverpool, MaCCI Summer Institute, Mannheim, Oxford, Pompeu Fabra, Tel Aviv, and Tilburg. We thank Andres Pechy, Toby Webber, and Yihan Yan for excellent research assistance.

# 1 Introduction

“There is perhaps no aspect of competition policy that is as controversial or has been as inconsistent over time and across jurisdictions as policy towards restraints between upstream firms and their downstream retailers.” [Lafontaine and Slade \(2008\)](#)

When manufacturers enter into exclusive agreements with their downstream customers, they restrict the ability of these customers to engage with upstream rivals. As a result, vertical restraints may hinder the viability of upstream firms, thereby reducing market competition. However, exclusive agreements can also foster competition by encouraging firms to improve service quality or secure investments, mitigating downstream free-riding problems.<sup>1</sup>

Empirically discerning whether these restraints promote or hinder competition is challenging.<sup>2</sup> Crucially, these effects may extend beyond the immediate parties to an agreement. The resulting *contracting externalities* ([Segal, 1999](#)) arise when a restraint imposed on one downstream customer indirectly alters the incentives of others. As noted by [Whinston \(2006\)](#), an upstream supplier may “induce a particular buyer or a subset of buyers to sign *[an exclusive deal]* because by doing this he can monopolize *other* buyers without paying them anything.” These forces are particularly salient in markets where a supplier’s ability to provide future support or upgrades is shaped by its current sales and scale. In such settings, extensive exclusivity with some buyers can weaken a rival’s effective viability market-wide, making its products less attractive even to buyers not directly subject to the restraints.<sup>3</sup>

In this paper, we investigate the understudied contracting externalities and persistent effects of exclusive agreements, focusing on how restraints targeting specific buyers alter competitors’ incentives and market outcomes. We examine Intel’s alleged agreements with personal computer (PC) firms as a case study. During the period under study (2002–2009), the x86 microprocessor

---

<sup>1</sup> As a result, in the US, exclusive dealing is not *per se* illegal; rather, each case is evaluated under the “rule of reason” standard, as reaffirmed in *Tampa Elec. Co. v. Nashville Coal Co.*, 365 U.S. 320 (1961). While exclusive dealing may violate Section 3 of the Clayton Act and Section 2 of the Sherman Act, its *per se* illegality was rejected in *Standard Oil Co. v. United States (Standard Stations)*, 337 U.S. 293, 305–06 (1949). For further discussion of the competitive effects and legal treatment of exclusive dealing in the US, see [Areeda and Kaplow \(1997\)](#).

<sup>2</sup> [Asker \(2016\)](#) develops empirical tests to distinguish procompetitive from foreclosure motives in vertical contracts. [Fumagalli and Motta \(2017\)](#) examine the application of price-cost tests to loyalty discounts and exclusive dealing arrangements. They show that contracts referencing rivals, that is, contracts in which the terms depend on how much the buyer sources from competing suppliers, can serve as a powerful exclusionary tool and facilitate buyer-specific discrimination by dominant firms.

<sup>3</sup> [Atalay et al. \(2011\)](#) show that signals of supplier financial distress discourage purchases of durable goods, as consumers revise downward their expectations of receiving future services in the event of supplier bankruptcy. Our framework similarly incorporates downstream customers who reassess a supplier’s future viability.

market was dominated by two suppliers: Intel, with approximately 80% of the market share, and its smaller competitor, Advanced Micro Devices (AMD), accounting for most of the remaining 20%. These suppliers provided essential components, Central Processing Units (CPUs), to a downstream oligopoly of PC manufacturers, including Dell, HP, and Toshiba. From late 2002 until 2007, Intel engaged in various exclusive or near-exclusive deals with PC manufacturers in the CPU market, including, among others, conditional rebates, the exclusion or delayed launch of AMD-based machines, and market-share-based contracts.<sup>4</sup> These practices attracted significant scrutiny from antitrust authorities worldwide, as well as from AMD, resulting in billions of dollars in fines and settlements.

To organize the analysis, we first outline a simple two-period conceptual framework of downstream sourcing in which AMD’s future “viability”, capturing its effective ability to supply, invest, and be perceived as a credible long-run supplier, depends on current adoption. Intel can offer exclusive or near-exclusive contracts to selected buyers in the first period. Excluding some buyers reduces AMD’s current sales, lowers its subsequent viability, and thereby depresses other buyers’ incentives to adopt AMD in the next period. This framework formalizes the notion of contracting externalities in our setting: exclusivity with one set of buyers generates negative spillovers on others through the dynamic viability channel. We derive predictions about (i) the direct effect of restraints on targeted product lines or buyers and (ii) cross-buyer spillovers when restraints are imposed on other lines or firms, which we take to the data.

We use information from litigation to construct quantitative indices measuring the extent of exclusionary restraints in Intel’s transactions with specific customers. We match these indices with market-level data on PC and CPU unit sales to calculate, for each PC brand over time, the share of PCs equipped with AMD processors. We combine this information with data on each CPU supplier’s technological advancement and production capacity. Finally, we develop separate quantitative indices that measure the intensity of antitrust activity against Intel over time.

Using these data, we analyze the relationship between exclusive agreements, downstream technology adoption, and upstream capacity-related factors. Specifically, we estimate dynamic panel models of product line-level AMD adoption that allow for rich unobserved heterogeneity and dynamic persistence, and we exploit both internal (lag-based) instruments and external instruments based on antitrust activity to address the endogeneity of Intel’s restraints.

First, we find robust evidence that Intel’s contractual practices directly depress AMD adoption on targeted product lines. The dynamic estimates show that own-line restraints have economically meaningful effects in the short run: an additional restraint lowers AMD’s share on the treated

---

<sup>4</sup> While some of the contractual forms used by Intel were not, *de jure*, exclusive – meaning they would not strictly trigger breach if a PC firm sourced outside Intel – they were designed to induce exclusivity or near-exclusivity by threatening the loss of benefits for downstream firms through credible threats. More details are provided in Section 3.

product line by 0.22–0.40 percentage points (roughly 2–4% of the average adoption level). Because sourcing decisions are highly persistent, these short-run effects magnify substantially over time. The implied long-run reductions range from roughly 2.4 to 2.8 percentage points evaluated at the sample means of the restraint indices, corresponding to about 20–30% of the average AMD adoption level across product lines.

Second, we present novel evidence of contracting externalities. We distinguish between *standard* restraints (which count the number of restraints imposed on a downstream PC firm in a given quarter) and *extreme* restraints (those that effectively preclude meaningful AMD adoption). Restraints imposed on *other* firms generate sizable spillovers: in our preferred specifications, an additional standard restraint imposed on any competing firm reduces other firms' AMD purchases by 0.1 percentage points in the short run, while an additional extreme restraint reduces purchases by 0.3 percentage points. At prevailing restraint intensity—where product lines face, on average, more than 10 standard and nearly 4 extreme cross-firm restraints—these estimates imply market-wide short-run reductions of 0.6 to 1.3 percentage points. These effects are amplified over time, with long-run reductions of 0.4 percentage points per additional standard restraint and 2.6 percentage points per additional extreme restraint (roughly 4% and 25% of AMD's average share). At typical observed restraint levels, these per-unit effects imply market-wide reductions of roughly 4 percentage points for standard restraints and 10 percentage points for extreme restraints.

The results are robust to a wide set of checks, including placebo tests on the timing of restraints and alternative specifications such as first-difference IV models. Across all specifications, the evidence consistently shows both direct exclusion and substantial cross-buyer spillovers. Taken together, these patterns provide consistent empirical evidence of contracting externalities: exclusivity directed at some buyers reduces AMD's effective viability and thereby lowers adoption even among buyers not directly subject to the contractual provisions.

While contracting externalities have been recognized in theory, empirical evidence has been largely absent. This paper provides, to our knowledge, the first direct measurement of these spillovers in a major industrial setting. The results demonstrate that exclusionary contracts can meaningfully alter market outcomes not only for targeted buyers but also for firms that never enter into such agreements. These findings underscore that effective antitrust scrutiny of exclusive dealing must look beyond bilateral contracting partners and consider the broader market-wide consequences of dynamic viability effects.

**Related Literature** Our paper contributes to the literature on vertical restraints by quantifying contracting externalities and the persistent competitive dynamics of exclusive contracts. We show how these restraints distort downstream input choices not only through direct contractual terms but also by altering rivals' capacity investments and triggering self-reinforcing expectations

about supplier viability. In the theoretical literature, such contracting externalities are the primary mechanism through which exclusive dealing becomes anticompetitive: restraints imposed on some buyers weaken a rival's viability, thereby distorting other buyers' adoption incentives. Our empirical results document this mechanism in practice.

The competitive effects of exclusive dealing have been debated since the Chicago School critique, which dismissed the view that these contracts could be used by a firm to exclude a rival (Posner, 1976). Post-Chicago models demonstrate several mechanisms through which exclusive deals may generate anticompetitive effects. A first channel is the *coordination/threshold* mechanism: in Rasmusen et al. (1991), refined by Segal and Whinston (1996, 2000), entry requires the entrant to secure a minimum number of buyers to cover fixed costs.<sup>5</sup> When entry is viable only at a minimum scale, an incumbent can exploit buyers' lack of coordination to profitably exclude rivals, even when overall market foreclosure is incomplete. Consequently, signing an exclusive contract imposes a negative contracting externality on the rest. This mechanism closely aligns with Intel's alleged practices, where partial exclusivity agreements with PC manufacturers may have prevented AMD from achieving the minimum efficient scale needed to compete effectively in the CPU market.

A second, complementary channel is cross-market rent extraction in *noncoincident markets*: Bernheim and Whinston (1998) and Whinston (2006) show how exclusives in one relationship shift bargaining positions and surplus extraction in related markets, creating contracting externalities beyond the directly contracted market.

More recent theoretical contributions have incorporated dynamics and asymmetric information to further explain when exclusivity is likely to harm competition. Calzolari and Denicolò (2013, 2015) develop a framework in which exclusive contracts can be anticompetitive when one firm holds a dominant position. They argue that if the dominant firm's competitive advantage is sufficiently large, it can impose exclusivity without fully compensating buyers, as rivals may not be able to offer competitive alternatives. This is consistent with Intel's ability to maintain its market share despite AMD's technological improvements, a prediction our empirical results substantiate. Dynamic considerations amplify these concerns: reducing a rival's profits today increases its probability of exit tomorrow (Cabral and Riordan, 1994), while buyers' expectations about a supplier's future viability can depress current demand and reinforce foreclosure (Katz and Shapiro, 1985).<sup>6</sup>

Exclusion can also be implemented via practices that do not carry a contractual obligation of exclusivity, such as resale price maintenance, loyalty rebates, and lump-sum payments to transfer industry profits to retailers and induce them not to accommodate efficient upstream entry. Asker and Bar-Isaac (2014) show how such vertical practices can facilitate exclusion. In the Intel litigation,

---

<sup>5</sup> Fumagalli and Motta (2006) extend this work to settings with buyer-retailers, with downstream competition moderating exclusion.

<sup>6</sup> A related strand of work examines how incumbents sustain dominance through preemptive innovation (Gilbert and Newbery, 1982).

plaintiffs alleged that Intel employed lump-sum rebates conditional on hardware manufacturers' loyalty, amid growing competition from AMD microprocessors. These payments were described as a "bribe" to secure Intel's market dominance, with the implicit threat that greater reliance on AMD chips would lead to the withdrawal of these rebates.<sup>7</sup> In [Asker and Bar-Isaac \(2014\)](#), the threat is plausible as the equilibria indicate that, upon entry by a rival, Intel lacks the incentive to continue such payments, causing downstream firms to lose this revenue stream if they shift to the entrant's products. [DeGraba and Simpson \(2013\)](#) propose a similar theory of harm when discussing the Intel case. Similarly, [DeGraba \(2013\)](#) models "naked exclusion" – exclusionary conduct lacking any efficiency justification – in which dominant firms pay buyers to foreclose smaller rivals, showing that exclusives or near exclusives can lead to anticompetitive outcomes even if the rival remains in the market and is profitable. This model illustrates how a dominant firm (Intel) can maintain its market power by limiting the rival (AMD) access to downstream markets. Complementing this mechanism, [Chao et al. \(2018\)](#) demonstrate that all-units discounts, that is, retroactive rebates that apply once a threshold purchase share is met, can act as a partial foreclosure device: they raise the dominant firm's profits and market share while reducing the rival's, even without explicit exclusivity clauses. These results highlight how pricing-based vertical restraints can produce foreclosure effects akin to those generated by formal exclusive contracts.

In sum, contemporary theories recognize multiple mechanisms, including coordination failures, spillover effects, and asymmetric information, through which exclusive dealing can strategically foreclose competitors. Of course, no theoretical model can account for all the complex features of the Intel-AMD case and the microprocessor industry at once.

Empirically, the effects of exclusivity are mixed and context-dependent, with identification complicated by endogenous contract choice. Efficiency rationales appear in beer distribution ([Sass, 2005](#); [Asker, 2016](#)), while anticompetitive effects are documented in automobiles and retail ([Nurski and Verboven, 2016](#); [Ater, 2015](#)). [Hortaçsu and Syverson \(2007\)](#) find little foreclosure evidence in cement, emphasizing the importance of productivity differences. [Conlon and Mortimer \(2021\)](#) find that quantity-based "vertical rebates", similar to the loyalty-based payments used by Intel, have foreclosure effects in the snack food market. Our paper complements this literature by documenting contracting externalities in a high-innovation, capacity-constrained technology market.

Finally, [Goettler and Gordon \(2011\)](#) analyze competition between Intel and AMD in the PC microprocessor industry using a dynamic oligopoly model with durable goods and endogenous innovation. They find that AMD's presence constrains Intel's prices, benefiting consumers, but may slow the overall rate of innovation. Their model does not directly incorporate specific contractual restraints, such as exclusivity agreements, and rationalizes AMD shares through strong Intel fixed

---

<sup>7</sup> State of New York v. Intel Corp., Complaint, §99 (S.D.N.Y. 2009), available at [https://www.intel.com/pressroom/legal/docs/NY\\_AG\\_v.\\_Intel\\_COMPLAINT.pdf](https://www.intel.com/pressroom/legal/docs/NY_AG_v._Intel_COMPLAINT.pdf).

effects. Their counterfactual analyses simulate scenarios with varying degrees of foreclosure. These simulations show that some level of foreclosure increases prices, but also leads to higher innovation rates and potentially higher consumer surplus, as the increase in innovation offsets the negative effects of higher prices. Their work highlights the complex trade-offs involved in antitrust policy regarding vertical restraints that motivate our analysis, while abstracting from the complexity of contracting externalities, which is the focus of our work.

The remainder of the paper is organized as follows. Section 2 develops the conceptual framework. Section 3 describes the data and institutional background. Section 4 presents the empirical strategy. Section 5 reports the main results. Section 6 presents robustness checks. Section 7 concludes.

## 2 A Framework of Contracting Externalities in the CPU market

We present a simple two-period framework of downstream customers’ sourcing choices that captures how exclusivity with some buyers can depress a rival supplier’s future viability and, through that channel, other buyers’ incentives to adopt the rival. Our motivation follows the idea of contracting externalities in [Bernheim and Whinston \(1998\)](#).

We consider two upstream firms, an incumbent (Intel) and a smaller rival (AMD), serving a set of downstream buyers  $i \in \mathcal{I}$ . To aggregate buyers’ adoption into AMD’s overall period-1 demand, we assign each buyer a weight  $\theta_i > 0$ , normalized so that  $\sum_{i \in \mathcal{I}} \theta_i = 1$ . These weights scale buyers’ sourcing decisions into AMD’s total period-1 sales, which in turn determine its next-period viability.

AMD enters the first period with an initial viability state  $S_1 \geq 0$ , which captures AMD’s overall ability to supply and compete in future periods (capacity, financial strength, perceived reliability). Viability evolves endogenously with period-1 AMD sales.

Each individual buyer represents only a small fraction of AMD’s global demand. We therefore treat each  $i \in \mathcal{I}$  as an “atomistic” buyer whose own sourcing decision has a negligible effect on the aggregate state  $S_2$ . Buyers are forward-looking, but because their individual choices do not affect  $S_2$ , each buyer’s continuation value is independent of its period-1 sourcing choice. This implies that buyers do not internalize how their own sourcing contributes to AMD’s future viability, yielding a clean maximal benchmark for uninternalized contracting externalities. By contrast, Intel’s contracting strategy makes clear that, in aggregate, these decisions are material for AMD’s viability. We return to the implications of this assumption in the model discussion at the end of the section.

Time is  $t = 1, 2$ . In each period  $t$ , AMD’s quality or price–performance advantage relative to

Intel is denoted by  $\Delta Q_t \in \mathbb{R}$  and is common knowledge. If buyer  $i$  sources a share  $w \in [0, 1]$  from AMD when viability is  $S_t$ , its reduced-form flow payoff is:

$$\pi_{it}(w; S_t) = \alpha \Delta Q_t w - (\kappa_0 - \kappa_1 S_t) w - \phi w^2,$$

where  $\alpha > 0$  scales the value of AMD's advantage;  $\kappa_0 > 0$  and  $\kappa_1 > 0$  capture how viability reduces switching and operational frictions; and  $\phi > 0$  is a convex adjustment-cost (inertia) parameter.

AMD's viability updates once between periods according to:

$$S_2 = S_1 + \eta \sum_{j \in \mathcal{I}} \theta_j w_{j1}, \quad (1)$$

where  $\eta > 0$  measures the sensitivity of future viability to AMD's aggregate period-1 sales,  $\sum_{j \in \mathcal{I}} \theta_j w_{j1}$ .<sup>8</sup> This captures the idea that current adoption builds scale, financial strength, and reputation, reinforcing AMD's competitive position. In the Intel–AMD context, capacity constraints and scale economies make this feedback particularly salient: lower period-1 sales limit AMD's ability and incentive to expand production and R&D, weakening its credibility as a long-term supplier.

Intel's second-period profit  $\Pi_{I2}(S)$  is continuously differentiable and strictly decreasing in AMD viability,  $\Pi'_{I2}(S) < 0$ . Intel's first-period profit depends on its contracts and sales; it is summarized below.

The timing of the game is as follows:

1. The initial state  $(S_1, \Delta Q_1, \Delta Q_2)$  is common knowledge.

2. Intel offers each buyer  $i$  a take-it-or-leave-it exclusivity contract specifying a transfer  $T_i$  (rebate or lump sum). If buyer  $i$  accepts, it commits to exclusive sourcing in period 1 (i.e.,  $w_{i1} = 0$ ) and receives the transfer  $T_i$ . If it rejects, it sources freely and receives no transfer.

3. In period 1, each buyer  $i$  who rejects exclusivity chooses  $w_{i1} \in [0, 1]$ ; those who accept choose  $w_{i1} = 0$ . Period-1 payoffs are realized, and transfers  $T_i$  are paid to accepting buyers.

4. AMD's viability evolves according to equation (1).

5. In period 2, all buyers simultaneously choose  $w_{i2} \in [0, 1]$  without contractual restrictions. Industry profits are  $\pi_{i2}(\cdot)$  for buyers and  $\Pi_{I2}(S_2)$  for Intel.

---

<sup>8</sup> We choose a linear and deterministic specification for simplicity and tractability. A more general law of motion could incorporate depreciation, concavity (diminishing returns to scale), or a minimum viable scale threshold, the latter making exclusion disproportionately powerful if it keeps AMD below critical mass. Our simple form captures the core feedback mechanism while providing a clear benchmark for the contracting externality.

The solution concept is subgame-perfect equilibrium, solved by backward induction.

In period 2, given  $S_2$ , buyer  $i$  chooses  $w_{i2}$  to maximize  $\pi_{i2}(w; S_2)$ . Because  $\pi_{i2}(\cdot; S_2)$  is strictly concave, the unique interior optimum satisfies:

$$w_{i2}^{\text{int}}(S_2) = \frac{\alpha \Delta Q_2 - (\kappa_0 - \kappa_1 S_2)}{2\phi}.$$

The best response is therefore:

$$w_{i2}^*(S_2) = \begin{cases} 0, & w_{i2}^{\text{int}}(S_2) \leq 0, \\ w_{i2}^{\text{int}}(S_2), & 0 < w_{i2}^{\text{int}}(S_2) < 1, \\ 1, & w_{i2}^{\text{int}}(S_2) \geq 1, \end{cases} \quad \frac{\partial w_{i2}^*}{\partial S_2} = \begin{cases} \frac{\kappa_1}{2\phi}, & 0 < w_{i2}^{\text{int}}(S_2) < 1, \\ 0, & \text{otherwise.} \end{cases}$$

In period 1, for a buyer not bound by exclusivity, the same reasoning yields:

$$w_{i1}^{\text{int}}(S_1) = \frac{\alpha \Delta Q_1 - (\kappa_0 - \kappa_1 S_1)}{2\phi}, \quad w_{i1}^*(S_1) = \begin{cases} 0, & w_{i1}^{\text{int}}(S_1) \leq 0, \\ w_{i1}^{\text{int}}(S_1), & 0 < w_{i1}^{\text{int}}(S_1) < 1, \\ 1, & w_{i1}^{\text{int}}(S_1) \geq 1. \end{cases}$$

If the buyer accepts exclusivity,  $w_{i1} = 0$  by contract. Payoffs are normalized so that sourcing exclusively from Intel ( $w_{i1} = 0$ ) yields zero payoff;  $\pi_{it}(w; S_t)$  is thus the incremental surplus from sourcing from AMD relative to this baseline.

Let  $\pi_{i1}^{\text{uncon}} \equiv \max_{w \in [0,1]} \pi_{i1}(w; S_1)$  and  $\pi_{i1}^{\text{excl}} \equiv \pi_{i1}(0; S_1) = 0$ . An exclusion offer ( $\text{EXCL}_i = 1, T_i$ ) is accepted if and only if

$$T_i \geq \pi_{i1}^{\text{uncon}}.$$

Intel, offering take-it-or-leave-it contracts, sets  $T_i^* = \pi_{i1}^{\text{uncon}}$  when exclusion is profitable.<sup>9</sup>

Let  $\mathcal{E} \subseteq \mathcal{I}$  denote the set of excluded buyers. Unconstrained buyers  $j \notin \mathcal{E}$  choose  $w_{j1}^*$ , while  $w_{j1} = 0$  for  $j \in \mathcal{E}$ . AMD's second-period viability is then

$$S_2(\mathcal{E}) = S_1 + \eta \sum_{j \notin \mathcal{E}} \theta_j w_{j1}^*.$$

---

<sup>9</sup> If contracts cap  $w_{i1} \leq \bar{w}_i$  rather than require  $w_{i1} = 0$ , we can simply replace  $w_{i1}^*$  by  $\min\{w_{i1}^{\text{int}}(S_1), \bar{w}_i\}$  throughout. The signs of the profitability condition, the externality, and all comparative statics are unchanged, though the effects become weak when the cap binds.

Intel's total profit under the exclusion set  $\mathcal{E}$  is:

$$\Pi_I(\mathcal{E}) = \Pi_{I1}(\mathcal{E}) + \Pi_{I2}(S_2(\mathcal{E})),$$

where  $\Pi_{I1}(\mathcal{E})$  denotes Intel's total period-1 profit from sales to all buyers (both excluded and non-excluded) net of any transfers  $T_i^*$  paid to excluded buyers. We treat  $\Pi_{I2}$  as a reduced-form profit function capturing Intel's improved future market power when AMD is weaker.

**Profitability of excluding buyer  $i$ .** Should Intel offer an exclusivity contract to buyer  $i$ , or let the buyer buy freely? Intel's total profit changes if it excludes buyer  $i$  are:

$$\Delta\Pi_I(i) = \underbrace{\left(\Pi_{I1}^{\text{excl } i} - \Pi_{I1}^{\text{no-excl } i}\right)}_{\text{change in period-1 profit}} + \underbrace{\left(\Pi_{I2}(S_2^{\text{excl } i}) - \Pi_{I2}(S_2^{\text{no-excl } i})\right)}_{\text{change in period-2 profit}},$$

where the first term captures the short-run cost of paying  $T_i^*$ , and the second term captures the long-run gain from lower AMD viability.

AMD's viability next period, holding the existing exclusion set  $\mathcal{E}$  fixed (and thus  $w_{j1} = 0$  for all  $j \in \mathcal{E}$ ), is:

$$S_2^{\text{no-excl } i} = S_1 + \eta(\theta_i w_{i1}^* + \sum_{j \neq i} \theta_j w_{j1}^*), \quad S_2^{\text{excl } i} = S_1 + \eta \sum_{j \neq i} \theta_j w_{j1}^*,$$

Excluding buyer  $i$  raises Intel's profit if  $\Delta\Pi_I(i) > 0$ , with  $T_i^*$  satisfying the buyer's participation constraint.<sup>10</sup>

**Equilibrium existence and characterization** Backward induction yields a subgame-perfect equilibrium. Each buyer's sourcing choice  $w_{it}^*(S_t)$  is unique in every period because the payoff function  $\pi_{it}(w; S_t)$  is strictly concave in  $w$ .

Because the exclusion decision is made over the finite family of subsets  $\mathcal{P}(\mathcal{I})$ , Intel's problem  $\max_{\mathcal{E} \subseteq \mathcal{I}} \Pi_I(\mathcal{E})$  admits an optimal solution  $\mathcal{E}^*$ .<sup>11</sup>

---

<sup>10</sup> Formally, Intel chooses an exclusion set of buyers. The marginal profitability  $\Delta\Pi_I(i)$  depends on which other buyers are excluded, so it may be positive for some exclusion sets and negative for others.

<sup>11</sup> Corner cases arise when the interior solution  $w_{it}^{\text{int}}(S_t)$  lies outside the feasible range  $[0, 1]$ . In such cases, the buyer's optimal share is truncated to the nearest boundary, that is,  $w_{it}^* = 0$  if  $w_{it}^{\text{int}}(S_t) \leq 0$  and  $w_{it}^* = 1$  if  $w_{it}^{\text{int}}(S_t) \geq 1$ . The comparative statics derived below remain valid in weak form: changes in parameters can no longer increase  $w_{it}^*$  beyond 1 or decrease it below 0, but the direction of effects (higher  $S_t$  increasing AMD adoption) continues to hold wherever the solution is interior.

**Comparative statics and contracting externalities** For interior solutions and a given exclusion set  $\mathcal{E}$ , period-2 AMD adoption by buyer  $i$  responds as follows:

$$\begin{aligned} \text{(i)} \quad & \frac{\partial w_{i2}^*}{\partial \Delta Q_2} = \frac{\alpha}{2\phi} > 0, \\ \text{(ii)} \quad & \frac{\partial w_{i2}^*}{\partial \phi} = -\frac{\alpha \Delta Q_2 - (\kappa_0 - \kappa_1 S_2)}{2\phi^2} < 0, \\ \text{(iii)} \quad & \frac{\partial w_{i2}^*}{\partial S_2} = \frac{\kappa_1}{2\phi} > 0. \end{aligned}$$

Thus, (i) better AMD quality/price–performance increases adoption; (ii) greater inertia  $\phi$  dampens all responses and lowers adoption; and (iii) higher AMD viability  $S_2$  makes AMD more attractive to all buyers.

Most importantly, if Intel excludes buyer  $j$  in period 1,  $w_{j1}$  is forced to zero; AMD sells less, so  $S_2$  falls ( $S_2^{\text{excl } j} < S_2^{\text{no-excl } j}$ ). Others then reduce period-2 adoption purely through this viability channel. The discrete effect on any other buyer  $i \neq j$  is therefore:

$$\Delta w_{i2}^* = w_{i2}^*(S_2^{\text{excl } j}) - w_{i2}^*(S_2^{\text{no-excl } j}) = -\frac{\kappa_1}{2\phi} \eta \theta_j w_{j1}^* \leq 0,$$

strictly negative whenever  $w_{j1}^* > 0$  and  $w_{i2}^*$  is interior. With a set  $\mathcal{E}$  excluded, the externality adds up linearly:

$$\Delta w_{i2}^* = -\frac{\kappa_1}{2\phi} \eta \sum_{j \in \mathcal{E}} \theta_j w_{j1}^* \leq 0.$$

Exclusivity with a large or would-be early adopter ( $\theta_j$  high,  $w_{j1}^*$  large) suppresses AMD’s short-run sales, weakens its subsequent viability, and, absent any direct restraint on them, tilts other buyers away from AMD in the future.

Excluding buyer  $i$  is therefore profitable for Intel if the future gain from lowering  $S_2$  exceeds the period-1 sacrifice (including the participation transfer):

$$\left( \Pi_{I1}^{\text{excl } i} - \Pi_{I1}^{\text{no-excl } i} \right) + \left( \Pi_{I2}(S_2^{\text{excl } i}) - \Pi_{I2}(S_2^{\text{no-excl } i}) \right) > 0, \quad \Pi'_{I2}(S) < 0.$$

This is the dynamic foreclosure logic. Exclusive contracts reduce AMD’s period-1 sales, weaken its viability  $S_2$ , and, through reduced scale, lower all buyers’ incentives to adopt AMD in the next period. The resulting decline in second-period adoption is a *contracting externality*: a negative cross-buyer spillover generated by dynamic feedback rather than direct information exchange. In our reduced-form setup, excluding some buyers depresses  $S_2$ , which, in turn, makes AMD less attractive to all other buyers. This captures the central cross-buyer spillover that, in richer models with endogenous reservation transfers, can make exclusion decisions strategic complements and give rise to “divide-and-conquer” dynamics as in the naked-exclusion literature (Rasmusen et al.,

1991; Segal and Whinston, 2000).<sup>12</sup>

Table 1 summarizes the model’s comparative statics. These derivatives characterize buyers’ period-2 best responses holding the exclusion set  $\mathcal{E}$  fixed.<sup>13</sup> In the empirical analysis, we abstract from the specific channels through which viability evolves and focus instead on how exclusivity-induced changes in  $S_t$  generate cross-buyer spillovers in future adoption.

Table 1: Comparative Statics of Period-2 AMD Adoption

| Parameter / Shift                                            | Effect on $w_{i2}^*$ (interior) | Interpretation                                                   |

|--------------------------------------------------------------|---------------------------------|------------------------------------------------------------------|

| $\uparrow \Delta Q_2$                                        | Positive                        | Higher AMD advantage increases adoption                          |

| $\uparrow \phi$                                              | Negative                        | Higher switching frictions dampen responsiveness                 |

| Exclude buyer $j$ in $t = 1$<br>( $w_{j1}^* \rightarrow 0$ ) | Negative                        | Contracting externality via lower AMD future viability ( $S_2$ ) |

**Discussion** This framework provides a simple baseline for understanding contracting externalities in vertical markets. The assumption that individual buyers behave atomistically and do not meaningfully affect AMD’s future viability  $S_2$  is a useful benchmark. The assumption implies that a buyer’s decision has no measurable effect on  $S_2$ ; when deciding whether to accept Intel’s exclusivity offer, a buyer only considers its own direct period-1 product loss, without internalizing the effect of its own adoption on AMD’s long-run position. The entire viability externality is therefore uninternalized and operates fully across buyers.

In the PC market, only a very small number of extremely large buyers were sufficiently important for their sourcing decisions to plausibly influence AMD’s perceived viability. For example, the European Commission notes that “*Fujitsu-Siemens, which in 2006, although it was the next largest OEM [original equipment manufacturer] after IBM in terms of market share, saw itself as too small to legitimise AMD for enterprise*”.<sup>14</sup> The Commission’s notion of “legitimization” directly parallels the viability channel in our model: AMD’s ability to compete in the future requires achieving sufficient scale and visibility today.

<sup>12</sup> In particular, our setup is conceptually related to Doganoglu and Wright (2010), who study exclusive dealing in the presence of network effects. In our framework, dynamic “viability” spillovers play a role analogous to network effects: early exclusive contracts reduce AMD’s viability, which, in turn, lowers AMD’s attractiveness to other buyers.

<sup>13</sup> In principle, sufficiently large parameter changes could also alter the optimal exclusion set  $\mathcal{E}^*$ , which would then shift  $S_2$  and  $w_{i2}^*$ . Such general-equilibrium adjustments are outside the scope of these local comparative statics.

<sup>14</sup> European Commission (2009), Intel Decision, Recital 1588.

Intel’s conduct is consistent with this asymmetry. Its most restrictive conditional rebates were targeted precisely at large buyers; those firms may have, at least partially, internalized AMD’s future viability and therefore required stronger inducements to remain exclusive to compensate for both the lost period-1 surplus and the lost future benefit from a stronger AMD (see Section 3). This creates a coordination game among large buyers. If other large buyers are expected to stay non-exclusive and support AMD, then it is individually optimal to also support AMD. Conversely, if other large buyers are expected to take exclusivity and abandon AMD, then AMD’s future is doomed ( $S_2$  will be low). The large buyer then faces a prisoner’s dilemma: supporting AMD alone is costly and futile, so it becomes optimal to take Intel’s exclusivity payment. Intel’s strategy becomes about breaking this coordination, using high transfers and, for example, sequential offers to convince one pivotal large buyer to defect.<sup>15</sup> Our model abstracts from such internalization by large buyers, providing a clean benchmark for the fringe. Consistent with this benchmark, the empirical results in Section 5 indicate that the contracting externalities were driven significantly by the aggregated actions of this large fringe, as Intel’s strategy focused on securing the pivotal, large buyers whose choices could tilt the ecosystem in Intel’s favor.

Second, we abstract from the possibility that contracts are renegotiated over time or that buyers interact strategically. In practice, renegotiation could allow Intel to renew or adjust exclusives, and strategic behavior among buyers could influence who accepts exclusivity and when.

Third, in our framework, AMD is not a strategic actor: its quality advantage ( $\Delta Q_t$ ) is exogenous, and it does not adjust pricing, capacity, or R&D in response to Intel’s contracts or its own viability. These decisions are obviously central to the competitive dynamic. Making  $\Delta Q_2$  a function of  $S_2$ , so that greater viability improves AMD’s future quality, would strengthen the feedback loop and could create nonlinear thresholds reinforcing our dynamic foreclosure logic.

Finally, the framework abstracts from downstream market growth (which we control for in the empirical analysis). If growth occurs for products outside Intel’s exclusive contracts, AMD may scale despite partial foreclosure; if growth occurs inside the contracted products, the dynamic feedback is stronger because the incumbent captures a growing base of demand.

---

<sup>15</sup> The State of New York case discusses downstream incentives as a

[...]“prisoner’s dilemma”: If all of the OEMs had been willing to deal with AMD without Intel-imposed restrictions, the resulting strengthened competition would have benefited them all, as well as consumers, by lowering their microprocessor costs. Nevertheless, there were strong — often overwhelming — incentives for any individual OEM to accept the pay-offs — and avoid the punishments — which Intel dealt out.

## 3 Data

We analyze the US market for CPUs from 2002 until mid-2009, a period during which Intel's relationship with prominent downstream customers was characterized by exclusive deals and vertical restraints. We focus on CPUs installed in personal computers purchased by US consumers in the home and business segments.<sup>16</sup> Sales to the home and business segments account for the majority of PC sales. Our dataset combines multiple sources, including information on PC and CPU sales and attributes, CPU manufacturers' production capacity, restraints characterizing Intel's vertical contracts, and the scope of the global legal action taken in connection with these restraints.

We estimate dynamic panel models to capture the impact of Intel's vertical restraints on downstream PC firms' adoption of AMD technology. Our unit of observation is the combination of a PC firm (e.g., Acer), brand (e.g., Aspire D), market segment (Home or Business), and quarter (from 2002:1 to 2009:2), resulting in around 3,800 observations.

### 3.1 PC Makers' Adoption of AMD and CPU Quality

We obtained quarterly PC and CPU sales data from Gartner Group. Table 2 reports descriptive statistics for PCs. During this period, there are 30 PC firms and 169 PC brands, yielding 204 unique firm-brand combinations. Sales are split almost evenly between home and business segments. The largest PC producers are Dell (31% market share) and HP (22%). There are no close competitors; however, a few firms have market shares between 5% and 10% (on average), including Acer, Fujitsu Siemens, Gateway, Lenovo, IBM, and Toshiba. PC prices vary widely, ranging from \$138 to \$3,218.<sup>17</sup> Over 60% of PCs sold are mobile devices (e.g., laptops, notebooks, ultraportables).

We define a product line as a firm–brand–segment (home/business) combination. We observe the CPU firm (e.g., AMD) and model (e.g., Athlon 64 X2) associated with each product line. The dependent variable is the share of sales in a product line-quarter with an AMD chip installed. For example, Acer's Aspire D was sold to home consumers in 2006:2. Some of these were equipped with an AMD Athlon 64 chip and others with an Intel Celeron chip.

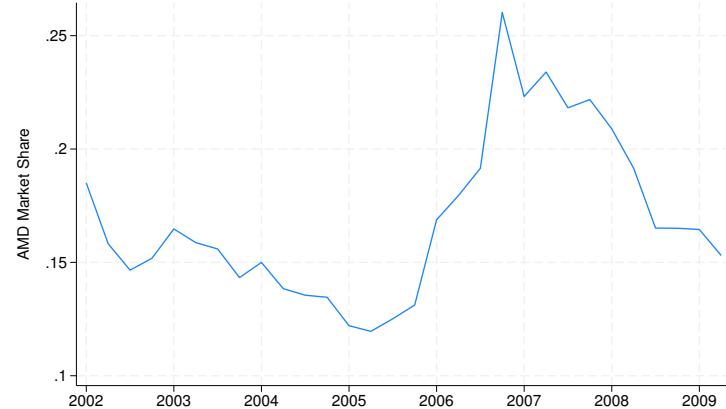

About 22% of PCs sold over the period were equipped with an AMD chip. Figure 1 shows the evolution of the market share of AMD over time. A noticeable increase occurs around 2006, when AMD's share rises from around 12% to over 25%. This gain, however, was temporary, and AMD's share declined to 15% by 2009. We discuss several developments that occurred during that time,

<sup>16</sup> We exclude Apple products as those exclusively used IBM's chips during much of the sample period. We also do not include servers, as server sales were not recorded in the dataset before 2005. However, we do record exclusionary restraints on the use of AMD chips in servers and incorporate those into the analysis. As explained below, this is consistent with the institutional background: market participants believed that adopting AMD chips in servers could have important spillovers into other market segments, such as desktops.

<sup>17</sup> We compute the average price by dividing revenue by the number of units.

Table 2: PC Descriptive Statistics

|                       | Mean | Std. Dev. | Min  | Max   |

|-----------------------|------|-----------|------|-------|

| PC Price (100\$)      | 7.73 | 4.02      | 1.38 | 32.18 |

| Sold in Home Market   | 0.46 | 0.50      | 0.00 | 1.00  |

| Mobile PC             | 0.61 | 0.49      | 0.00 | 1.00  |

| No. of PC Firms       | 30   |           |      |       |

| No. of PC Brands      | 169  |           |      |       |

| No. of Product Groups | 204  |           |      |       |

| No. of CPU Models     | 26   |           |      |       |

| PC contains AMD CPU   | 0.22 | 0.41      | 0.00 | 1.00  |

*Notes:* All variables expressed in monetary terms were deflated using the quarterly consumer price index (Bureau of Labor Statistics, base year 2000). A product group is a PC firm–PC brand combination.

including technological trends and strategic changes in the competitive arena, as well as changes in the intensity of exclusive restraints.

Figure 1: AMD Market Shares

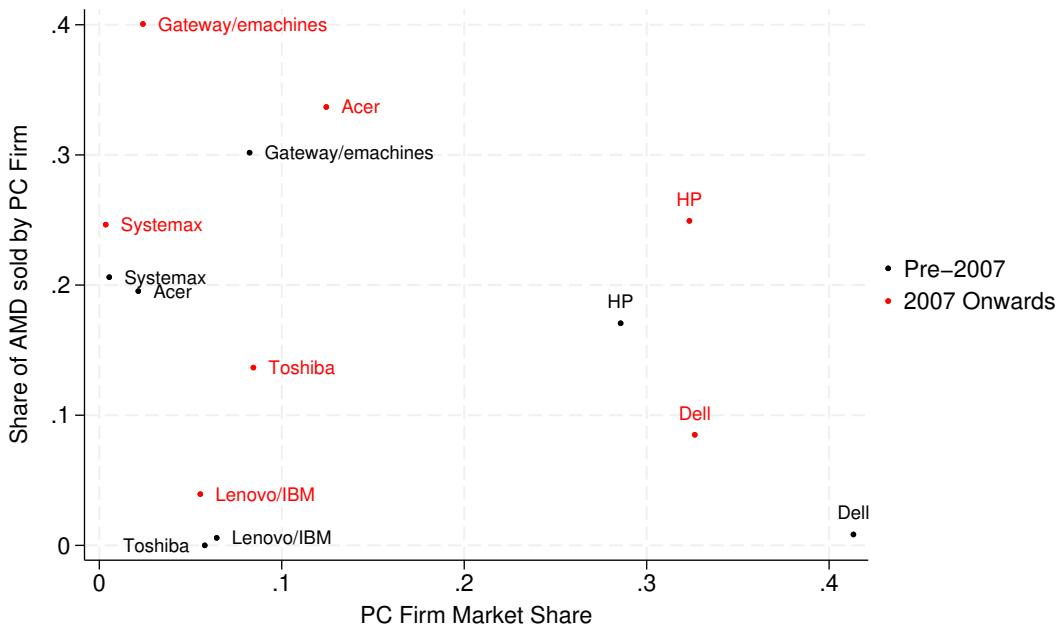

Figure 2 presents AMD’s market share for selected PC firms, along with these firms’ respective shares of the PC market before and after 2007.<sup>18</sup> While some firms continued with exclusivity into 2007, Dell discontinued its exclusive arrangements with Intel in late 2006. Figure 2 shows an increase in AMD adoption at the beginning of 2007 across *all firms*, where the rate of increase varies substantially. This shift reflects, in part, the removal of exclusivity restrictions. For instance, Dell, Lenovo, and Toshiba offered virtually no AMD-based systems before 2007 due to their exclusive

<sup>18</sup> Several mergers occurred in the industry: Gateway/emachines merged in 2004 and subsequently merged with Acer in 2007. Lenovo and IBM merged in 2005.

agreements with Intel.<sup>19</sup> However, the data also exhibit an increase in AMD adoption among firms *not* bound by exclusivity with Intel in the earlier sample period. Systemax, for example, expanded its AMD offerings post-2007 despite never facing Intel-imposed restraints. This suggests the presence of contracting externalities or other competitive forces unrelated to exclusive restraints. We explore this in detail through our estimation approach, designed to disentangle these contracting externalities from other forces.

Figure 2: AMD Purchases by Selected PC Firms

Panel A of Table 3 presents descriptive statistics for the CPUs sold in each PC. We obtained CPU prices from Instat and published list prices.<sup>20</sup> As shown in the table, Intel chips were, on average, 35% more expensive than their AMD counterparts. The subsequent rows demonstrate that this price premium does not reflect superior Intel quality. To measure quality, we use a continuous measure of the CPU model performance (the benchmark) obtained from Passmark.<sup>21</sup> The benchmark for Intel chips was, on average, 13% lower than AMD chips.

<sup>19</sup> Internal documents revealed in litigation showed that Intel's financial support was often conditioned on exclusivity or near-exclusivity. A 2002 Dell document stated that the "...original basis for the fund is...Dell's loyalty to Intel," meaning "no AMD processors." Similarly, an HP executive wrote in a 2002 email: "PLEASE DO NOT...communicate to the regions, your team members, or AMD that we are constrained to 5% AMD by pursuing the Intel agreement."

<sup>20</sup> Instat "Intel Rosetta Stone: Intel Processor Shipments, Forecasts, Technology and Roadmaps" Nov 2005.

<sup>21</sup> Accessed from [www.cpubenchmark.net](http://www.cpubenchmark.net). Details are provided in Appendix A1.

Table 3: Descriptive Statistics

|                                                             | Obs  | Mean  | Std. Dev. | Min   | Max   |

|-------------------------------------------------------------|------|-------|-----------|-------|-------|

| <b>A. CPU Characteristics</b>                               |      |       |           |       |       |

| Price AMD CPU (100\$)                                       | 3600 | 1.04  | 0.64      | 0.19  | 5.43  |

| Price Intel CPU (100\$)                                     | 3858 | 1.40  | 0.52      | 0.20  | 3.77  |

| Benchmark AMD CPU (in 1000)                                 | 3600 | 0.78  | 0.47      | 0.27  | 3.50  |

| Benchmark Intel CPU (in 1000)                               | 3858 | 0.69  | 0.58      | 0.17  | 6.45  |

| CPU Benchmark/Dollar AMD                                    | 3600 | 9.88  | 8.03      | 1.27  | 39.33 |

| CPU Benchmark/Dollar Intel                                  | 3858 | 6.11  | 6.51      | 1.09  | 45.10 |

| Age AMD Brand                                               | 3600 | 6.59  | 4.29      | 1.00  | 23.00 |

| Age Intel Brand                                             | 3858 | 7.09  | 5.42      | 1.00  | 30.00 |

| <b>B. Capacity and Cashflow</b>                             |      |       |           |       |       |

| AMD Capacity Index                                          | 3858 | 7.61  | 3.72      | 3.00  | 13.00 |

| Intel Capacity Index                                        | 3858 | 31.56 | 6.47      | 23.00 | 44.00 |

| AMD Free Cash (100M\$)                                      | 3858 | 7.89  | 3.25      | 2.82  | 19.05 |

| <b>C. Antitrust Variables &amp; Exclusionary Restraints</b> |      |       |           |       |       |

| Num. Pending Antitrust Cases Against Intel                  | 3858 | 3.22  | 1.69      | 1.00  | 6.00  |

| Exclusionary Restraints Index                               | 1540 | 3.32  | 1.37      | 1.00  | 6.00  |

| Extreme Restraints Index                                    | 1540 | 1.30  | 0.68      | 0.00  | 3.00  |

| Intel Payments to Dell (M\$)                                | 744  | 579   | 396       | 0.00  | 1070  |

| Intel Payments to non-Dell PC Firms (M\$)                   | 3114 | 4.60  | 25.98     | 0.00  | 193   |

*Notes:* An observation is a product line-quarter combination. AMD (Intel) statistics are reported only over AMD-based (Intel-based) CPU models, hence the counts differ. The underlying CPU characteristics are aggregated to the product line-quarter level as described in Appendix A1.

The value delivered by chip manufacturers is captured by the benchmark-per-dollar metric (CPU benchmark score divided by CPU price). This indicates the superior value of AMD chips relative to Intel, which were 61% better in terms of this indicator. AMD's technological success is reflected, for example, in a New York Times article covering the State of New York antitrust case against Intel:

“In 2005, Michael S. Dell’s namesake company was getting pounded. His competitors were selling personal computers and servers built on cheap, popular and powerful chips from Advanced Micro Devices, while Mr. Dell had stuck loyally with slower chips from Intel. In an email note to Intel’s chief executive, Paul S. Otellini, Mr. Dell threatened to switch to A.M.D.”<sup>22</sup>

<sup>22</sup> “State Accuses Intel in an Antitrust Suit,” Ashlee Vance, New York Times, November 5 2009.

Likewise, a 2002 internal HP presentation noted that AMD’s Athlon desktop processor “had a unique architecture” and was “more efficient on many tasks,” adding that AMD offers “no-compromise performance at superior value.”<sup>23</sup>

However, in 2006, Intel introduced a new generation of Intel chips, specifically the Intel Core product family, which offered substantial improvements over incumbent generations. Indeed, the benchmark-per-dollar metric increases more rapidly in the latter part of the sample period for Intel, even surpassing AMD’s in some cases (e.g., the highest values of the benchmark-per-dollar metric for Intel are associated with core processors). The European Commission 2009 decision also notes this trend

“... Intel has made references to having recently ‘caught up’ with AMD following the launch of its new generation of CPUs based on the ‘Core’ micro-architecture.”<sup>24</sup>

Considering this information together with Figure 1, we obtain a preliminary view of a weak correlation between AMD’s product quality and its market share. AMD’s market share was relatively low in the earlier part of the sample, when it seemed to have had a better value proposition than that of Intel’s, but increased around the time that Intel started to compete along a technological edge. However, this pattern aligns with the timeline of Intel’s exclusivity arrangements, which we analyze next.

## 3.2 CPU Production Capacity

The production process in the microprocessor industry is multidimensional, and crucial inputs of productive capacity are disclosed in firms’ annual reports. These include the number of fabrication facilities (FABs), the silicon wafer size used at each FAB (larger wafers enable more simultaneous CPU production), and the integrated circuit (IC) process node (measured in nanometers, where smaller nodes allow both higher CPU yields per wafer and improved CPU power efficiency). Using this information, we construct a firm-level *capacity index*.

A firm’s capacity index is the yearly sum of rank points assigned to each FAB, where each FAB’s points reflect its wafer size and IC process node. Specifically, process nodes are ranked from largest to smallest in nanometers (with smaller nodes reflecting more advanced manufacturing capabilities), and wafer sizes are ranked from smallest to largest (larger wafers implying greater production capacity). Each FAB receives the sum of its two rank points, and the firm’s capacity index is the total of these points across all of its active FABs in that year. All rankings are performed within-year to reflect the evolving technology frontier, so the index increases with both the number of FABs a firm operates and the technological sophistication of those facilities.

---

<sup>23</sup> European Commission 2009 decision (COMP/C-3 /37.990 - Intel)

<sup>24</sup> European Commission 2009 decision (COMP/C-3 /37.990 - Intel)

Table 4: Upstream Production Capacity Over Time

| Year | Number of Fabs |       | Mean ICP in nm |       | Mean wafer in mm |       | Capacity index |       |

|------|----------------|-------|----------------|-------|------------------|-------|----------------|-------|

|      | AMD            | Intel | AMD            | Intel | AMD              | Intel | AMD            | Intel |

| 2002 | 1              | 10    | 130            | 150   | 200              | 220   | 3              | 28    |

| 2003 | 1              | 7     | 130            | 130   | 200              | 229   | 3              | 23    |

| 2004 | 1              | 7     | 130            | 113   | 200              | 243   | 3              | 27    |

| 2005 | 2              | 6     | 90             | 78    | 250              | 300   | 9              | 33    |

| 2006 | 2              | 5     | 90             | 75    | 250              | 300   | 9              | 28    |

| 2007 | 2              | 5     | 78             | 57    | 250              | 300   | 10             | 32    |

| 2008 | 2              | 7     | 65             | 60    | 300              | 300   | 12             | 44    |

| 2009 | 2              | 6     | 55             | 50    | 300              | 300   | 13             | 41    |

*Notes:* ICP stands for Integrated Circuit Process. The Fab capacity index is computed by ranking IC process (largest to smallest) and wafer size (smallest to largest), then summing these points over all fabs.

Table 4 shows the evolution of the processor makers' production technology and capacity over time.<sup>25</sup> AMD consistently lags behind Intel in both IC process technology and wafer size. In addition, capacity expansion required substantial capital expenditures; in 2007, constructing a single FAB required approximately \$5 billion (Brown and Linden, 2009). Using AMD's quarterly financial reports, we calculate AMD's quarterly free cash flow.<sup>26</sup> Panel B reveals that AMD's free cash in each quarter was, on average, \$789 million, significantly below the investment needed for new FAB construction. Industry analysts emphasize the significance of Intel's production capacity advantage. A blogger following the industry remarked in 2002 that

“...AMD knows that if they do only what they have announced in terms of their capacity expansion road map, they will allow Intel to retreat into the part of the market AMD can't supply, lick their wounds, and buy/or finish developing technology that can compete with AMD in a year or two.”<sup>27</sup>

The blogger's prediction may, in fact, have materialized. While AMD offered better price-to-performance value in 2002, Intel ultimately regained technological leadership in subsequent years. AMD's chronic production capacity constraints and insufficient capital reserves for expansion may have contributed to this reversal.

<sup>25</sup> We exclude pilot FABs and smaller FABs. Including these would further amplify Intel's capacity advantage.

<sup>26</sup> Data retrieved from <http://ir.amd.com/> on September 18, 2014.

<sup>27</sup> Source: “AMD's Future Fab Capacity,” a January 2002 post by ValueNut on the online community *The Motley Fool* (<http://www.lnksrv.com/community/pod/2002/020122.htm>, accessed on March 9, 2017). The original URL is no longer active.

### 3.3 Antitrust Activity and Exclusive Restraints

The primary explanatory variables measure the degree of contractual restraints associated with the buyer’s terms of trade with Intel, as well as those imposed on other buyers. To quantify these relationships, we construct variables capturing the nature of Intel’s vertical contracts. The main empirical challenge is the absence of a unified, authoritative source detailing all these contractual arrangements, which are not directly observed. Instead, we rely on information extracted from legal proceedings pertaining to Intel’s practices.

These cases include a private lawsuit by AMD and antitrust cases brought by the European Commission (EC), the Japanese Fair Trade Commission (FTC), the Korean FTC, the State of New York, and the United States FTC. These cases address Intel’s behavior over various time frames spanning 2002:4 to 2007:4. Additionally, we draw on information from the U.S. Securities and Exchange Commission (SEC) case against Dell. Although not an antitrust case, it centered on the allegation that Dell failed to disclose to investors that a substantial share of its operating income was derived from payments received from Intel in return for exclusivity. As such, the case provides insight into Dell’s exclusive relationship with Intel. According to the SEC’s complaint against Dell,

“Intel paid the computer maker rebates as part of a deal in which Dell agreed not to use microchips manufactured by Intel’s rival AMD. We’re not talking small change: The payments totaled \$4.3 billion between 2003 and 2006.”

Table 5 summarizes the timeline of legal actions against Intel. The cases differed in both scope and legal outcome. In 2005, the Japanese FTC issued a decision finding that Intel had obtained exclusivity or near-exclusivity from major Japanese PC manufacturers in violation of antitrust laws. Intel chose to comply with the decision by agreeing to refrain from certain practices, such as contractually requiring customers to use Intel chips exclusively. In 2009, Intel paid AMD \$1.25 billion to settle a lawsuit filed by AMD in 2005. The Korean FTC ruled against Intel in 2008 and rejected Intel’s appeal in 2013. The European Commission fined Intel €1.06 billion in 2009. This decision was upheld by the General Court in 2014, but, following Intel’s appeal, was partially annulled. In 2023, the Commission narrowed the scope of the case to include only naked restrictions and imposed a revised fine of €376 million. The naked restrictions involved Intel paying PC firms to halt or delay the launch of AMD products and to limit the sales channels available for AMD models. In the US, antitrust cases brought by the State of New York and the FTC were settled with minimal or no financial penalties.

**Antitrust Index** We use the case files to construct an index capturing the scope and magnitude of antitrust activity. The index records the number of pending antitrust cases brought against Intel

Table 5: Antitrust activity timeline

---

|      |                                                                                                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2001 | AMD files complaint with European Commission (EC)                                                                                                                                        |

| 2004 | Japan Fair Trade (FT) opens investigation                                                                                                                                                |

| 2005 | Japan FT issues decision that Intel violated rules; Intel complies<br>Korea FT opens investigation<br>AMD files lawsuits in Germany, Japan, and US                                       |

| 2007 | EC brings charges<br>Korea FT brings charges                                                                                                                                             |

| 2008 | State of New York opens investigation<br>US Federal Trade Commission (FTC) opens investigation<br>Korea FT decision that Intel violated antitrust law<br>Intel appeals Korea FT Decision |

| 2009 | EC decision that Intel violated rules; Intel appeals<br>State of New York files lawsuit<br>AMD cases against Intel end in settlement<br>US FTC brings charges                            |

| 2010 | US FTC case ends in settlement                                                                                                                                                           |

| 2012 | State of New York case ends in settlement                                                                                                                                                |

| 2013 | Korea FT upholds ruling against Intel appeal                                                                                                                                             |

| 2014 | EC decision of 2009 upheld by the court; Intel appeals                                                                                                                                   |

| 2022 | EC decision of 2009 partially annulled by the court                                                                                                                                      |

| 2023 | EC re-imposes fine based on narrowed scope                                                                                                                                               |

---

by AMD and regulators worldwide in the relevant quarter.<sup>28</sup> Panel C of Table 3 shows that, on average, there were 3.22 pending cases per quarter, with a maximum of 6 pending cases in 2008, quarters 2, 3, and 4. These case-count variables are used to characterize the legal environment and document antitrust pressure over time. In the estimation, we use underlying legal events, such as the opening of investigations, formal decisions, and statements of objection, as instruments for the restraint variables.

**Exclusionary Restraints Index** The case files reveal a variety of instruments through which Intel may have affected the adoption of AMD’s technology by downstream customers. We define,

---

<sup>28</sup> Information on the antitrust activity is obtained from Intel’s annual reports. For regulatory cases, we use the date on which a formal investigation was initiated as the case’s starting date. For AMD’s lawsuits, we used the filing date. The ending date is defined as either the date on which a decision was rendered by the relevant authority or court (regardless of whether the decision was later appealed) or the date of settlement, where applicable.

at the product-line-quarter level, binary indicators that equal one if an instrument was employed.<sup>29</sup>

Specifically, our analysis focuses on the following types of restraints: caps on the amount sold of AMD-based PCs; rebates conditional on the extent of purchases from AMD (i.e., conditional rebates); exclusion of AMD from certain product lines or delayed launches of specific AMD-based machines (i.e., a type of naked restriction); commitments to increase Intel's market share (i.e., the share of CPUs the client buys from Intel); restraints on the distribution channels that could be used to sell AMD-based products (i.e., another form of naked restriction); limitations on the marketing for AMD-based products; restraints imposed on bidding on contracts using AMD-based products; threats to withdraw or divert funding to rivals, or other forms of retaliation for selling AMD-based products; and guarantees of preferred access to Intel CPUs.<sup>30</sup>

Given the complex nature of the restraints, we again use an index approach to quantify their presence and track their temporal evolution.<sup>31</sup> Not all restraints are equally restrictive. Some practices limited AMD adoption at the margin, for example, by capping volumes or conditioning rebates on relative purchases, while firms could still offer AMD-based products. Other practices effectively eliminated AMD from a firm's relevant product space for a sustained period, either by imposing zero caps, excluding AMD from entire product lines, or threatening retaliation in response to AMD adoption. Because these latter practices are likely to have qualitatively different implications for both short-run adoption and longer-run competitive dynamics, we distinguish between *standard* and *extreme* restraints in our empirical analysis. Our measure of standard restraints counts the number of all restraints imposed on a downstream PC firm in a given quarter.

The second measure counts only those restraints we classify as *extreme*, defined as practices that effectively preclude meaningful AMD adoption within the affected product lines. These include: a zero-cap on AMD-based machines; exclusion from certain product lines or delayed launches of specific AMD-based machines; threats or retaliation; and commitments to increase Intel's share of the client's CPU purchases. We provide details on the construction of the index in Appendix A1.

---

<sup>29</sup> While the public documents contain rich information about Intel's restraints, they are not comprehensive. The text of the lawsuits often states that the listed practices are illustrative rather than exhaustive. The variables we construct to capture the restraints are, therefore, subject to measurement error. That said, the plaintiffs had an incentive to provide detailed information on what they believed to be the important aspects of these restraints, based on detailed internal documents. Moreover, to the extent that measurement error induces attenuation bias, our estimates can be interpreted as lower bounds on the true effects of the restraints. The fact that we nonetheless find substantial effects reinforces our conclusions.

<sup>30</sup> The latter benefit was particularly valuable to downstream customers. As one industry insider noted, "survival practically depends on being able to get allocations of the newest chips, which are always in short supply coming out of the gate." See [ZDNet \(Dell-AMD coverage\)](#). Furthermore, the State of New York case states: "Access to adequate and timely supply of products from Intel was a major concern for all OEMs, whose business was extremely time-sensitive."

<sup>31</sup> We should note that Intel has consistently denied these claims. Determining the legal status of such restraints is a matter for the courts. Our analysis uses these alleged restraints as an empirical context to explore their potential effects, conditional on their existence.

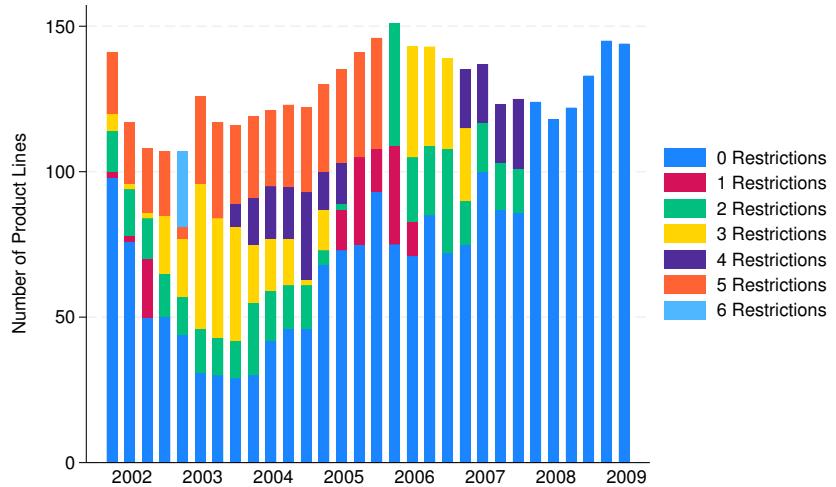

Panel C of Table 3 reports summary statistics. On average, there were 3.32 restraints in place per brand-segment-quarter and 1.30 extreme restraints. The maximum number observed in a single product line-quarter was six restraints, of which up to three were classified as extreme. Figure 3 shows the total count of product line data cells that were affected by different numbers of restraints over the sample period. This count was high early in the sample period, and later declined; no restraints are observed after 2007. This pattern provides sharp temporal variation in the deployment of restraints. The cross-sectional variation at the firm level is also substantial: the case files identify the start and end dates of restraints for each PC firm, and the number and intensity of restraints vary significantly across firms, as well as in their timing.

Figure 3: Evolution of restraints Imposed by Intel

Examples of this variation are abundant. As previously noted, restraints affecting Japanese customers began in 2002 but abruptly ended in 2005, when Intel decided to comply with the Japanese authorities' ruling. Additionally, Intel applied different restraints across customers and market segments. For example, HP faced limits on the number of AMD-based machines it could sell in the business sector. The distribution of these restraints across customers and segments is not random; however, our empirical strategy addresses this endogeneity concern.

The decline in the prevalence of restraints in the later part of the sample, particularly the absence of any restraints after 2007, may be traced to increased antitrust activity. This interpretation aligns with contemporaneous accounts. For example, the SEC case against Dell states:

“(Dell executives) ...also understood that the Intel...payments were at risk because of the near continuous scrutiny directed at Intel by various competition authorities around the world and, to the degree that...payments were deemed anticompetitive, such payments could abruptly end.”

In other words, market participants appear to have believed that the rise in antitrust scrutiny had a chilling effect on Intel’s restraints on AMD adoption. The escalation in regulatory pressure thus created a quasi-natural experiment that led to a sharp decline in the deployment of restraints, helping identify their potential impact.

One possible concern is that the observed decline in restraints may partly reflect truncation error: while our product market data extends through mid-2009, some of the legal documents we rely on are dated earlier, raising the possibility that restraints may have persisted after 2007 but are simply not observed in our data. This concern can, however, be rather easily dismissed. The documents underlying our analysis cover the entire relevant period. Although the AMD lawsuit was filed in 2005, other legal proceedings provide documentation extending into later years. For example, the FTC case against Intel, settled in 2010, includes a May 2010 memorandum describing Intel’s actions in 2008 and 2009.<sup>32</sup> However, those actions pertain to products such as GPUs, chipsets, and compilers, rather than to CPUs. The document does not specify CPU-related restraints after 2007, strengthening the credibility of our index, which falls to zero beginning in 2008. The European Commission’s 2009 decision explicitly covers the period 1997-2007 and draws on evidence collected during site inspections at Intel and several European PC retailers in February 2008. This decision further supports the notion that the restraints were concentrated earlier in the sample period: “Most of the individual abuses concerned are concentrated in the period ranging from 2002 to 2005, whilst, after the end of 2005, at most two individual abuses occur simultaneously at any given point in time.” The State of New York case, filed in November 2009, also provides corroborating information. Many of these legal proceedings contain overlapping evidence, and none report CPU-related restraints persisting beyond 2007.

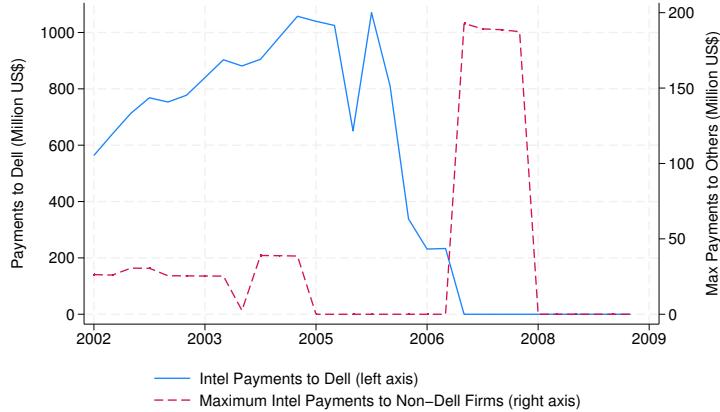

We also observe rebates offered by Intel to PC firms via the “Intel Inside” program. The exact amounts paid to Dell are available from the SEC’s case *SEC v. Dell Inc.* (July 22, 2010), which covers the period from 2003 to 2006. These payments were substantial and deviated markedly from Intel’s public description of the program, which claimed that 3% of the CPU costs would be rebated to PC manufacturers to finance advertising for PC models equipped with Intel CPUs. For the period after 2007, we compute Intel’s payments to Dell as 3% of Dell’s CPU costs, computed using Gartner sales data and the price dataset described previously. We apply the same 3% methodology to estimate payments to other PC firms throughout the sample period. This variable is defined at the firm level and aggregated over all brands and segments.

Figure 4 provides an overview of these payments. Payments to Dell are displayed on the left axis, while the maximum payments to other PC firms appear on the right axis. Payments to Dell were nearly 100 times the amount the firm should have received under the advertised 3% rebate. For other PC firms, the average per-quarter per-firm payment varied over time between \$2.3 and

---

<sup>32</sup> See [FTC \(2010\) Memorandum](#).

\$5.5 million, with maximum payments ranging between \$50 and \$200 million.

Figure 4: Evolution of Intel's Payments to PC Firms

### 3.4 Data Patterns

A few patterns emerge from the data during the period of heightened antitrust concern (2002:4 – 2007:4). First, the rate of adoption of AMD's technology increased significantly, though it declined again toward the end of the sample period (see Figure 1). Second, AMD's benchmark-per-dollar advantage began to erode as Intel regained a technological edge. Finally, around the same time, Intel's use of exclusionary restraints began to decline (see Figure 3). This joint data variation supports the hypothesis that Intel's restraints had previously slowed the adoption of AMD's technology: as the restraints were gradually phased out, AMD gained market share despite Intel's increasing technological advantage.

Another notable pattern is Intel's advantage in production capacity, which made it an unavoidable trading partner for downstream customers. This capacity advantage enabled Intel to engage in exclusive dealing, an option that was not available to AMD, given its inability to meet 100% of a customer's demand on its own. The 2009 State of New York case against Intel stated that

“(a)ll major computer manufacturers depend on Intel in a variety of ways and are reliant on it for microprocessors, since AMD is, and in the foreseeable future will remain, unable to fulfill more than a small share of their requirements.”<sup>33</sup>

Furthermore, as discussed in Section 2, Intel did not need to engage in exclusive deals with all clients as

<sup>33</sup> Source: Intel NYAG Complaint

“The flip-side of large [PC firms]’ importance in legitimising a product is that smaller [PC firms] are not able to do so in the same way. This is explicitly recognised by one such [PC firm], Fujitsu Siemens, which in 2006, although it was the next largest [PC firm] after IBM in terms of market share ... expressed concerns vis-à-vis AMD that it saw itself ‘as too small to legitimize AMD for enterprise.’” <sup>34</sup>

This suggests that contracting externalities may have played a role in the adoption of AMD technology.

In addition, the fact that antitrust scrutiny expanded concurrently with the phasing out of exclusive restraints raises the possibility that increasing regulatory pressure was an important factor in curbing Intel’s exclusionary practices. Anecdotal evidence cited above also indicates that downstream customers may have interpreted the heightened antitrust activity as a predictor of future reductions in Intel’s exclusionary restraints, thereby increasing their current willingness to adopt AMD technology.

## 4 Econometric Framework

### 4.1 Empirical design

Our empirical setting exploits a panel of PC firm–brand–segment combinations (e.g., Acer’s Aspire D line for the business segment), defined as product lines and indexed by  $i$ ; we observe them across quarterly time periods  $t = 1, \dots, T$ . We estimate the following dynamic specification:

$$w_{it} = \rho w_{i,t-1} + \beta_p p_{it} + \beta_c c_t + \beta_x x_{it} + \beta_r^{\text{own}} r_{it}^{\text{own}} + \beta_r^{\text{riv}} r_{it}^{\text{riv}} + \mu_i + \tau_t + \varepsilon_{it}, \quad (2)$$

where the dependent variable  $w_{it}$  denotes the fraction of product line  $i$ ’s sales with an AMD chip installed at time  $t$ .<sup>35</sup> The term  $\mu_i$  captures time-invariant unobserved heterogeneity at the PC firm–brand–segment level,  $\tau_t$  is a quarterly time trend, and  $\varepsilon_{it}$  is an idiosyncratic error term.<sup>36</sup>

The right-hand-side variables capture the observable drivers of downstream firm adoption decisions at the product line level:

**Lagged AMD share,  $w_{i,t-1}$ :** The inclusion of the lagged share term captures the path-dependent dynamics of product  $i$  adoption. Firms with prior AMD integration benefit from learning-by-doing and leverage existing production-line investments, thereby reducing the marginal

<sup>34</sup> European Commission 2009 decision (COMP/C-3 /37.990 - Intel)

<sup>35</sup> When  $c_t$  and  $x_{it}$  are vectors,  $\beta_c c_t$  and  $\beta_x x_{it}$  denote the corresponding inner products.

<sup>36</sup> We estimate a dynamic panel model rather than a structural model. While this limits our ability to simulate counterfactual scenarios, it allows us to flexibly control for rich product-level heterogeneity without incurring the computational cost associated with a large state space.

cost of subsequent AMD adoption. Switching between Intel and AMD is costly as chips are not “pin compatible,” and platform transitions involve sunk costs. Consequently, higher values of  $w_{i,t-1}$  are expected to increase the probability of continued AMD utilization.

**PC prices,  $p_{it}$ :** For each product  $i$  in quarter  $t$ , we compute the sales-weighted average prices across PC models. Any other time-invariant PC characteristics are absorbed by the fixed effect  $\mu_i$ . AMD technology may be especially attractive in certain lines, for example, in low-margin “value” products using cost-efficient AMD processors.

**CPU manufacturing capacity and liquidity,  $c_t$ :** The vector  $c_t$  includes AMD’s and Intel’s global manufacturing capacity indices and the lagged amount of free cash available to AMD. Capacity reflects long-run FAB investment decisions, such as facility count, wafer size, and process technology, that evolve slowly and do not respond to quarter-level fluctuations in U.S. product line adoption. These indices capture medium-run supply availability and thus proxy for the constraints relevant to PC manufacturing, which operates with minimal inventories and requires reliable within-quarter chip deliveries. Because capacity is global while our dependent variable reflects U.S.-specific adoption, any feedback from  $w_{it}$  to capacity would operate only through longer-run profitability and is unlikely to occur within the quarter. We include AMD liquidity because AMD faced tighter financing constraints than Intel, which affected its ability to sustain production and reliably supply customers.